Updated April 18, 2023

Introduction to Verilog vs VHDL

Verilog and VHDL are the hardware description languages that are used for the generalized purpose which are further accepted and supported by a various synthesis and verification tools. In this article, we will first study the two languages and further observe what are the differences between them by referring to the comparison table. In this topic, we are going to learn about Verilog vs VHDL.

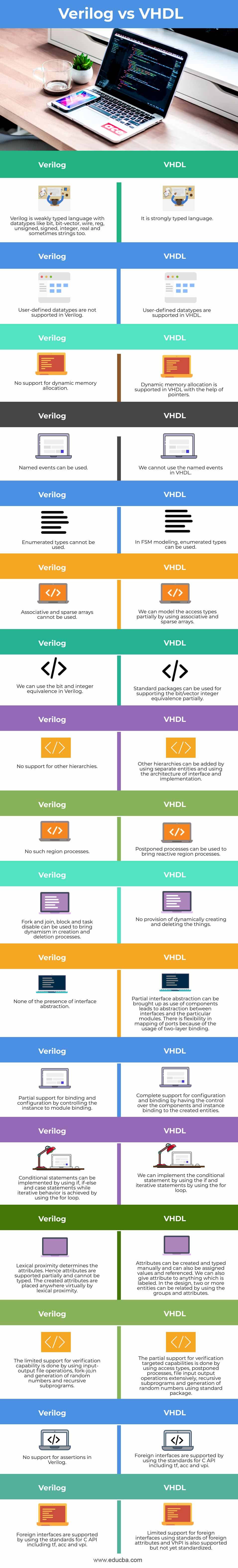

Head to Head Comparison Between Verilog vs VHDL (Infographics)

Below are the top differences between Verilog and VHDL

Key Difference between Verilog vs VHDL

Let us discuss some of the major key differences between Verilog vs VHDL

Verilog

The Verilog is actually derived from the C programming languages and Hilo which is an old hardware description language. It is a very limited and weakly typed language that has all the predefined data types in it. The datatypes are represented in bit-level. Other data types like strings can be mixed with the Verilog. There is very ambiguous simulation semantics in Verilog as compared to VHDLs. As a result of this, the developers find Verilog very flexible but there is a drawback of the resulting race conditions due to ambiguity if guidelines are not followed while coding. It is very difficult to provide the reusability function of packages because of the limited scope of language and incapable packaging capability.

There is a provision of basic simulation control commands in Verilog which help to do the system tasks. Command-line or batch simulations are used by the Verilog developers because of predefined system tasks and simple data types and debugging can be done by seeing waveforms from the simulation.

VHDL

VHDL is actually a derivation of the Ada programming language which is a very richly typed and strongly typed hardware description language. As compared to the Verilog which is another HDL, VHDL is very verbose because of the language requirement which also adds up to the additional self-documenting designs. The strong- typing for VHDL also makes sure that datatypes are converted explicitly from one to another like for example bit-vector to an integer. The VHDL language was designed in a manner that will make the semantics of the language very unambiguous and clear. The designs of VHDL are easily portable which also adds up the functionality to move from one tool to another very easily. Due to this, there is no necessity to be concerned about race conditions.

The VHDL design is mostly dependent on the IEEE standard 1164 and also refers to the Math and Numeric packages in order to make the utility of language more enhanced. There is no provision of monitoring capabilities or simulation control in VHDL’s as they are completely tool-dependent. Interactive GUI’s are used for debugging because the types are user-defined in VHDLs and also there is no presence of in-built simulation control which makes the design problems debugged even harder.

Comparison Table of Verilog vs VHDL

The following table demonstrates the detailed comparison between the Verilog and VHDL in detail –

| Verilog | VHDL |

| Verilog is weakly typed language with datatypes like bit, bit-vector, wire, reg, unsigned, signed, integer, real and sometimes strings too. | It is strongly typed language. |

| User-defined datatypes are not supported in Verilog. | User-defined datatypes are supported in VHDL. |

| No support for dynamic memory allocation. | Dynamic memory allocation is supported in VHDL with the help of pointers. |

| Named events can be used. | We cannot use the named events in VHDL. |

| Enumerated types cannot be used. | In FSM modeling, enumerated types can be used. |

| Associative and sparse arrays cannot be used. | We can model the access types partially by using associative and sparse arrays. |

| We can use the bit and integer equivalence in Verilog. | Standard packages can be used for supporting the bit/vector integer equivalence partially. |

| No support for other hierarchies. | Other hierarchies can be added by using separate entities and using the architecture of interface and implementation. |

| No such region processes. | Postponed processes can be used to bring reactive region processes. |

| Fork and join, block and task disable can be used to bring dynamism in creation and deletion processes. | No provision of dynamically creating and deleting the things. |

| None of the presence of interface abstraction. | Partial interface abstraction can be brought up as use of components leads to abstraction between interfaces and the particular modules. There is flexibility in mapping of ports because of the usage of two-layer binding. |

| Partial support for binding and configuration by controlling the instance to module binding. | Complete support for configuration and binding by having the control over the components and instance binding to the created entities. |

| Conditional statements can be implemented by using if, if-else and case statements while iterative behavior is achieved by using the for loop. | We can implement the conditional statement by using the if and iterative statements by using the for loop. |

| Lexical proximity determines the attributes. Hence attributes are supported partially and cannot be typed. The created attributes are placed anywhere virtually by lexical proximity. | Attributes can be created and typed manually and can also be assigned values and referenced. We can also give attribute to anything which is labeled. In the design, two or more entities can be related by using the groups and attributes. |

| The limited support for verification capability is done by using input-output file operations, fork-jo,in and generation of random numbers and recursive subprograms. | The partial support for verification targeted capabilities is done by using access types, postponed processes, file input output operations extensively, recursive subprograms and generation of random numbers using standard package. |

| No support for assertions in Verilog. | Foreign interfaces are supported by using the standards for C API including tf, acc and vpi. |

| Foreign interfaces are supported by using the standards for C API including tf, acc and vpi. | Limited support for foreign interfaces using standards of foreign attributes and VhPI is also supported but not yet standardized. |

Conclusion – Verilog vs VHDL

Verilog is the HDL that is completely emerging and evolving in which new features are getting added continuously. VHDL is a strongly typed language and is very verbose while Verilog is a weakly typed language and has all the predefined datatypes with it. Simulation control is not supported by the VHDL internally as an in-built thing but Verilog has the facility of simulation support which helps in debugging the design-related problems easily with the help of waveforms that are displayed based on the database and can be analyzed further.

Recommended Articles

This is a guide to Verilog vs VHDL. Here we discuss the Verilog vs VHDL key differences with infographics and comparison table. You may also have a look at the following articles to learn more –